安装教程

1、从艾薇下载站下载软件压缩包,并进行解压处理

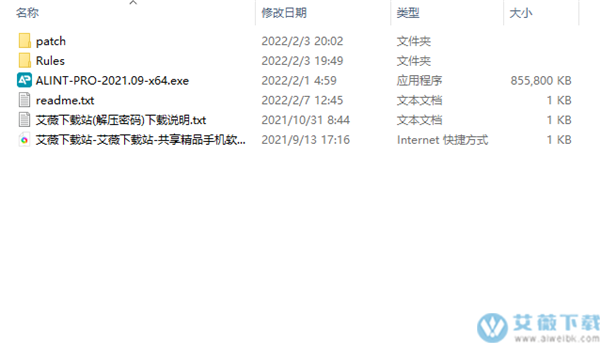

2、运行软件安装程序,设置软件安装路径

3、选择Aldec ALINT PRO 2021安装模式

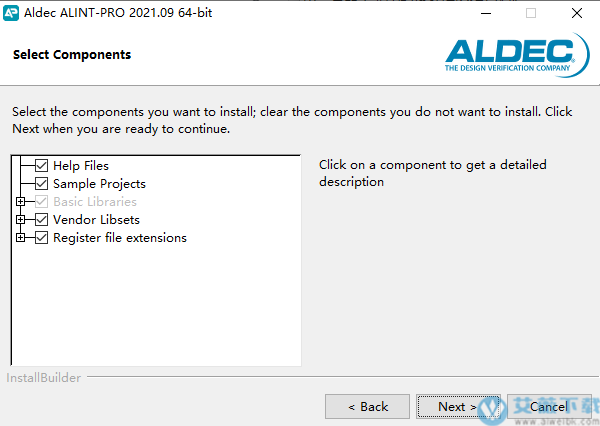

4、勾选需要安装的功能要件

5、等待安装完成

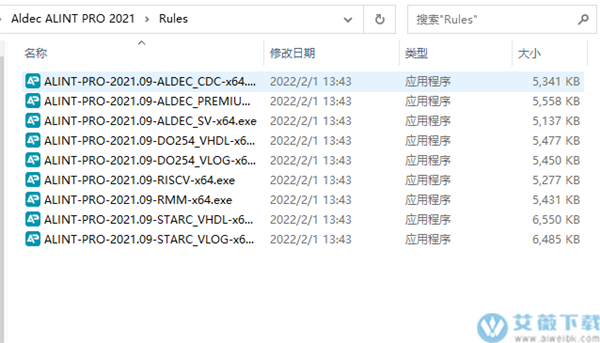

6、安装完成后,将Rules文件夹内的所有规则进行安装,路径默认指向软件安装路径

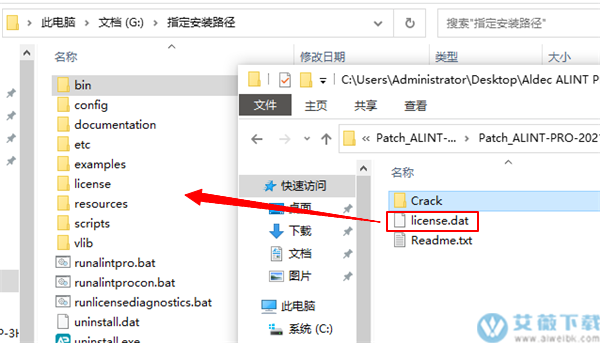

7、解压文件夹内的压缩包,将Crack内的文件复制到安装路径中的bin文件内

8、然后将license.dat复制到Aldec ALINT PRO 2021安装路径当中

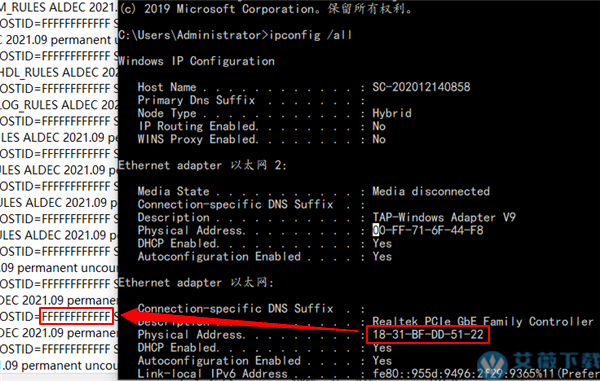

9、按Win+R,输入"cmd"打开命令控制台,然后输入"ipconfig /all"获取物理地址,以文本的方式打开license.dat,在文本当中选中"FFFFFFFFFFFF",按Ctrl+H将所有的"FFFFFFFFFFFF"替换成你的物

理地址,保存文件

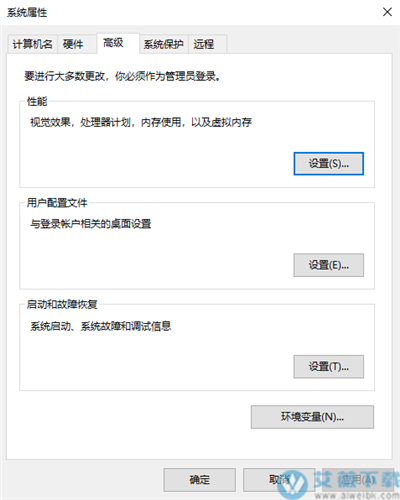

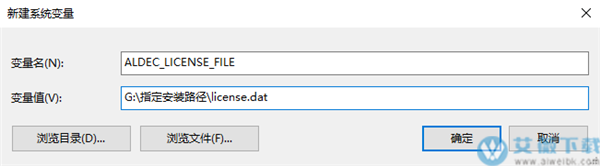

10、右键"此电脑"或“我的电脑”,点击属性,在点击高级系统设置,在高级页面中点击环境变量

11、创建环境变量,在变量名处填写"ALDEC_LICENSE_FIL"并将变量值指向安装路径当中的"license.dat",即可完成破解

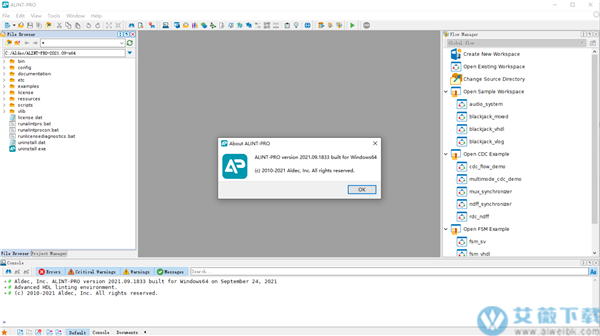

12、运行软件即可免费使用

软件特色

1、经行业验证的指南支持基于STARC(半导体技术学术研究中心)和RMM(重用方法手册)指南的规则检查,以利用主要半导体公司在设计开发中使用的最佳实践。

对于安全关键型设计,该软件提供DO-254规则插件,专注于设计稳定性,建议帮助实现符合DO-254标准的设计。

对于RISC-V设计社区,该软件提供了RISC-V规则插件,该插件基于经过行业验证的最佳IP设计实践和指南。

ALDEC Basic和Premium规则插件收集了客户和内部设计专家的综合知识,可以补充上述插件,而SV插件针对特定于SystemVerilog设计子集的新类型RTL错误。

该软件包含强大的策略编辑器,可根据设计需求快速构建高效的规则配置。

2、CDC和RDC验证

该软件具有可选的ALDEC_CDC规则插件,可在单个产品中实现时钟和复位域交叉(CDC、RDC)的全部功能和RTL分析。

它通过基于断言和亚稳态仿真的动态检查来增强验证,并提供额外的调试功能,例如时钟和复位域的示意图突出显示,以及浏览检测到的域交叉和识别的同步器。

3、DFT验证

该软件支持一组专用规则,用于在RTL设计阶段验证来自外部端口的时钟和复位可控性,从而使后续设计阶段的设计测试更容易。

4、设计约束设置

该软件可以读取先前为综合和静态时序分析工具创建的现有SDC™约束文件。该工具还可以根据拓扑分析自动生成初始SDC模板,包括主时钟和生成时钟、I/O延迟和异步时钟组的定义

5、设计约束扩展

该软件提供了对设计约束的自定义扩展,一种易于阅读且直接的块级约束格式,用于描述不可综合的行为模块、具有受保护代码的IP模块、供应商库单元等。使用约束来描述模块的接口用等效模型替换网表中的黑匣子,从而实现精确的linting。还可以描述设计人员对复位控制、自定义同步单元和安全CDC路径(包括具有准静态源的路径)的意图。

6、框架

该软件提供了一个紧密集成的GUI框架,具有直观的界面和高效的问题分析手段。该框架包括许多视图:Schematic Viewer–提供完全综合网表的图形表示以及时钟域和违规路径突出显示。控制原理图以图形方式展示了时钟和复位之间的关系。

CDC Schematics是域交叉和同步器的专用可视化;时钟和复位查看器——显示时钟和复位网络以及它们传播通过的所有引脚和网络;违规查看器——通过各种标准启用违规过滤,添加豁免,交叉探测到HDL和示意图,并允许访问摘要数据。

Active-HDL™、Riviera-PRO™、Vivado™和Quartus™项目可以自动转换为ALINT-PRO格式,显着缩短设计设置时间。

软件功能

1、静态设计验证该软件是针对用VHDL、Verilog和SystemVerilog编写的RTL代码的设计验证解决方案,专注于验证编码风格和命名约定、RTL和综合后仿真不匹配、平滑和优化综合、正确的FSM描述、避免进一步设计阶段的问题、时钟和复位树问题、CDC、RDC、DFT以及可移植性和重用的编码。该解决方案基于RTL和SDC™源文件执行静态分析,在设计周期的早期发现关键设计问题,从而显着缩短设计签核时间。在RTL仿真和逻辑综合阶段之前运行该软件可防止设计问题蔓延到设计流程的下游阶段,并减少完成设计所需的迭代次数。

2、DRC和CDC/RDC分析的单一框架

该软件具有精心设计的直观框架,它提供了用于高效设计分析的功能,包括RTL原理图查看器、FSM查看器、时钟和复位查看器、控制原理图查看器、详细说明查看器、违规查看器以及CDC查看器等特殊工具,用于时钟和复位域交叉分析的RDC查看器和CDC原理图。

通过读取外部项目文件格式(Aldec Active-HDL、Aldec Riviera-PRO、Xilinx Vivado、Xilinx ISE、英特尔Quartus)、解释典型仿真脚本(兼容命令,如vcom、vlog、vsim、vlib)以及用于批处理模式工具的传统文件列表,以及用于直接导入单个文件和整个目录的非常简单的GUI向导。

3、全芯片级Linting与单元Linting

支持2种不同的linting方法:全芯片级linting和单元linting。两种方法相辅相成,通常应用于设计周期的不同阶段。

完整的芯片级linting运行整个设计层次结构的分析,通用参数的特定值从顶层实例传播到叶子模块,并应用用户定义的时序约束。这种方法对于典型的HDL linting工具来说是传统的,并且更经常在签核期间使用,或者用于需要将整个设计作为一个已经集成的系统同时探索的验证类型(时钟和复位检查、CDC、RDC、DFT)。这种方法假设整个或至少大部分被测设计已经实现。

单元linting是一种相对较新的方法,可以很好地与平面处理相结合模式——一种特殊的细化,它认为HDL设计单元彼此独立,并且使用通用参数的默认值。这种处理风格高度容忍设计中缺失的元素,例如层次结构中尚未实现的部分。这使得单元linting在应用于单个源文件时最有价值,独立于其他文件,以及在设计人员修改文件之后。因此,许多非常有价值的规则检查很早就启用,甚至几乎在编写代码之后立即启用,从而将设计人员的反馈循环从几天或几周压缩到几秒钟。单元linting的一个自然应用是与HDL编辑器的集成,单元linting在后台运行,

单元linting并不能消除使用完整传统linting的需要,因为独立单元的组合可能会在集成后产生额外的问题。但是,系统地应用单元linting可以显着减少签核期间的验证量。

4、检查FPGA设计

该软件以最少的设置顺利地支持针对使用Xilinx、Altera、Microsemi和Lattice技术的FPGA实现的设计运行规则检查。提供最新版本的FPGA供应商库,这些库是预先构建的、默认安装的,并且预先配置用于高级时序和CDC规则检查。

该软件为基于IP的FPGA设计自动设置分层和增量分析流程。每个IP块可以首先单独分析,提取的时序约束可以被提升和重新用于更快的更高级别的设计分析。除非在原始设计环境中重新配置IP块,否则它的主体只分析一次,从而在主FPGA设计的后续运行中节省大量时间。

5、批处理模式流

还可以通过一组丰富的基于TCL的脚本命令访问关键的功能。这些脚本可用于自动化设计规则检查、重复设置和报告生成。这些脚本可以在交互式控制台shell或全自动批处理模式下运行。最后,该软件能够使用单个命令行shell应用程序调用以真正的批处理模式运行最典型的设计输入和linting场景,这使得它非常适合与更大的回归测试脚本和持续集成环境集成,例如詹金斯。

6、可用规则库

该软件包括基于STARC(半导体技术学术研究中心)和RMM(重用方法手册)设计指南的规则库,它利用了世界各地半导体公司在设计开发中使用的最佳实践。对于安全关键设计,该软件提供基于DO-254指南的规则库,专注于影响设计稳定性的关键问题分析。对于RISC-V设计社区,该软件提供了RISC-V规则插件,该插件基于经过行业验证的最佳IP设计实践和指南。

主要规则插件辅以高度可配置的Aldec Basic和Premium规则库,这些规则库由该软件在FPGA和ASIC数字设计方面的内部经验驱动,并包括现有客户推荐的许多附加功能,以对抗芯片杀手工业规模设计中的问题。SV插件针对特定于SystemVerilog设计子集的新型RTL错误。

ALDEC_CDC规则插件将该软件转变为全面的CDC和RDC验证解决方案,能够在现代多时钟和多复位设计中进行复杂的时钟和复位域交叉分析和亚稳态问题的处理。该软件中的验证策略由三个关键要素组成:静态结构验证、设计约束设置和动态功能验证。前两个步骤在该软件中执行,而动态检查通过与模拟器(Riviera-PRO™、Active-HDL™)的集成来实现,和ModelSim®支持)基于自动生成的测试平台。这种方法揭示了RTL模拟过程中潜在的亚稳态问题,否则将需要检测实验室测试。CDC和RDC问题的调试是通过丰富的原理图和HDE交叉探测机制以及综合报告和基于TCL的API实现的,允许浏览综合结果、时钟和复位结构、检测时钟和复位域交叉,并识别同步器。

软件亮点

1、时钟和复位网络分析2、避免 RTL 后和综合后仿真不匹配

3、验证 FSM 描述的正确性

4、提取的 FSM 和已识别的 FSM 问题的图形探索

5、代码可移植性和重用

6、使用 ALDEC_CDC 规则插件进行广泛的 CDC 和 RDC 检查

7、高级 CDC 和 RDC 调试环境

8、原理图查看器

9、DFT 检查

10、SDC™ 支持

11、IP描述的设计约束扩展

12、后台和批处理运行模式

使用说明

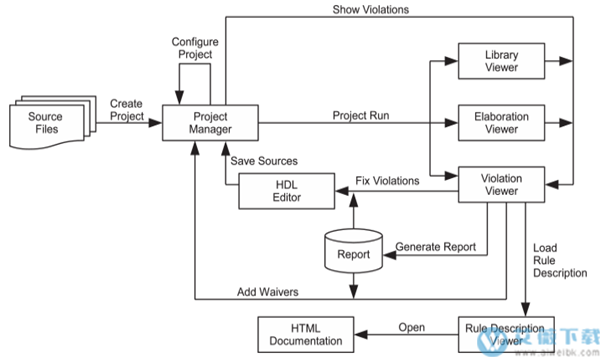

1、面向项目的流程在Aldec ALINT PRO 2021中,需要一个项目来执行设计分析。如果不将它们添加到项目中,就不可能处理单个文件。在解析、细化、综合、约束和linting阶段生成的数据与项目紧密集成,并旨在与项目一起使用。这适用于GUI和控制台工作流程。常见的工作流程如图所示。

面向项目的流程

首先,应使用专用的项目管理器窗口创建项目/工作区。

然后可以执行项目运行。它包括连续的设计输入和linting阶段,也可以单独启动。成功运行项目后,可以在Violation Viewer窗口中观察到linting结果。

Project Manager、Library Viewer和Elaboration Viewer窗口可用于过滤Violation Viewer中显示的违规。分析违规后,应修复源代码,并且可能需要添加一些豁免。

为了在不涉及产品框架的情况下分析违规行为,可以生成独立报告。

控制台窗口用于在设计输入和分析阶段进行故障排除。它包含阶段执行期间产生的错误和警告,以及指示进度的状态消息。HTML文档与控制台集成在一起-可以直接从控制台消息访问帮助页面。

Rule Description Viewer是一个专用窗口,显示有关在Violation Viewer窗口中选择的规则的附加帮助信息。

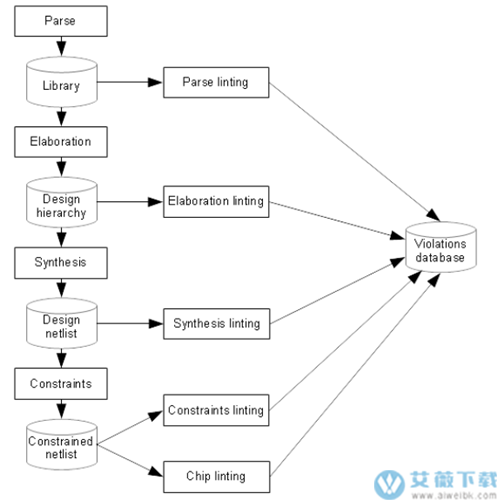

2、设计分析阶段

整个设计分析过程可以使用Run GUI选项或project.run命令启动。它由以下连续阶段组成,也可以使用GUI或控制台命令单独启动:解析、解析linting、精化、精化linting、综合、综合linting、约束、约束linting、芯片linting。

设计分析阶段

解析、细化、综合和约束阶段对应于设计输入。只有在所有先前的设计输入阶段都成功完成后,才能执行每个后续的设计输入阶段。

在解析阶段根据指定的语言标准对VHDL和Verilog/SystemVerilog源进行语法分析。该阶段的结果是可以在Library Viewer窗口中观察到的库。

细化阶段执行设计静态细化,这意味着将实例绑定到模块、解析库引用、展开生成语句、检查所有层次名称等。细化阶段的结果是在细化查看器中显示的设计层次结构树。

综合阶段产生网表生成。RTL原理图窗口是用于设计网表导航的图形工具。

在约束阶段,执行添加到项目的.sdc和.adc文件,将相应的设计约束应用于项目网表并执行高级网表分析。结果,生成了受约束的neltist并完成了设计输入。Clocks and Resets Viewer窗口显示在约束阶段发现的时钟和复位列表(在约束文件中指定和自动检测到的)。并且可以在CDC Viewer和RDC Viewer中相应地详细观察时钟和复位域。

在linting阶段执行设计分析。如果相应的设计输入阶段已成功完成(例如,解析linting需要执行解析阶段),则可以执行每个linting阶段。

linting是使用指定要求检查设计的过程。需求由一组通过linting策略配置的规则定义。根据检查所需的信息,将每个规则的检查分配给特定的linting阶段。

解析linting

词汇和语言级别的规则违规(注释、语言结构、编码风格、可读性等)。

细化棉绒

违反依赖于层次结构级别和参数值的规则(顶级单元的命名约定、位宽、表达式等)。

合成棉绒

与网表相关的规则违规(适当使用从HDL代码生成的逻辑元素)。

约束linting

违反检查设计约束的规则(时钟/复位树结构、错误路径、延迟等)。

切屑掉毛

违反依赖于时钟/复位树和供应商原语(CDC、DFT、设计结构等)的规则

设计分析的结果是存储在项目存储库中的违规行为。可以在“违规查看器”窗口中观察违规情况。

系统要求

支持的平台:Linux®(32/64 位)/Windows® 10/8.1/8/7(32/64 位)框架:GUI、交互式控制台和批处理模式宏、Tcl、Perl 脚本支持

支持的标准:Verilog® IEEE 1364(1995 和 2001),SystemVerilog® IEEE 1800(2005 和 2009),VHDL IEEE 1076(1987、1993、2002 和 2008)

规则库:ALDEC_BASIC(VHDL 和 Verilog)防止简单编码错误(命名、样式、格式等)的基本规则,ALDEC_RESTRICTIONS(VHDL 和 Verilog)

强烈推荐的规则旨在避免有害的芯片缺陷。

核心机制:时钟和复位自动检测,基于与时钟/复位引脚的直接连接和通过传播自动检测设计控制信号不同的生成模式。

读取和生成 SDC™ 约束:Aldec ALINT PRO 2021可以根据设计分析建议约束并考虑用户指定的约束。

许可部分:IP描述的设计约束扩展,设计约束的扩展,为工具提供有关没有 RTL 描述的单元的信息。